# Diseño de un LNA de baja potencia de Ultra Ancho de Banda (UWB) **CMOS** para IEEE 802.15.4z

## **Brian García Vega**

Dr. Francisco Javier del Pino Suárez, Dr. David Galante Sempere

GITT (Sistemas electrónicos), julio 2024

ESCUELA DE INGENIERÍA DE TELECOMUNICACIÓN Y ELECTRÓNICA

## INTRODUCCIÓN

En este proyecto se lleva a cabo el diseño a nivel de esquemático y de layout de un amplificador de bajo ruido (LNA) de banda ultra ancha (UWB) basado en transistores CMOS para el estándar IEEE 802.15.4z, utilizando la tecnología 45RFSOI.

#### **OBJETIVOS**

- Realizar un estudio teórico de los LNA para UWB para el estándar IEEE 802.15.4z.

- Diseñar el LNA que cumpla con los requisitos de UWB para el estándar IEEE 802.15.4z.

- Realizar la simulación y verificación del diseño.

### **METODOLOGÍA**

Se realiza un estudio teórico del estándar IEEE 802.15.4z y del estado del arte de LNA para este estándar. De este modo, se diseña el LNA acorde a las especificaciones del estándar. El diseño del LNA consta de dos partes:

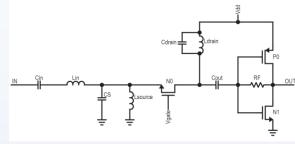

- <u>Diseño a nivel de esquemático</u>: se definen los componentes que conforman el circuito, empleando los establecidos en la tecnología 45RFSOI. Para ello, se realiza una comparación de rendimiento entre los transistores de la tecnología, seleccionando los más adecuados.

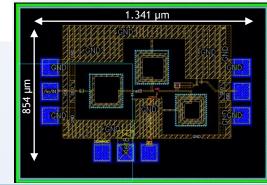

- Diseño de layout: tras tener el diseño del esquemático, se realiza el diseño físico del circuito, explicando el proceso de diseño.

Por último, se realiza una comparación de los resultados con el estado del arte

## Esquemático del LNA

# Layout del LNA

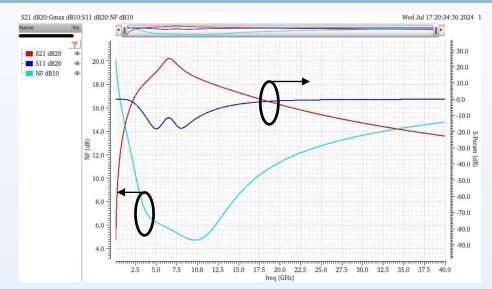

## **RESULTADOS**

Los resultados principales del LNA diseñado son:

|                           | Este Trabajo |

|---------------------------|--------------|

| Freq (GHz)                | 3,5-10,4     |

| Tecnología                | 45 nm S0I    |

| V <sub>DD</sub> (V)       | 0,9          |

| Máx. S <sub>21</sub> (dB) | 25,14        |

| S <sub>11</sub> (dB)      | < -10        |

| Mín. NF (dB)              | 5,68         |

| Consumo (mW)              | 4,93         |

| Área (mm²)                | 1,13         |

## **CONCLUSIONES**

En este Trabajo de Fin de Grado se ha realizado un estudio teórico de los conceptos básicos de los transistores MOS y de los LNAs, además de estudiar el estándar IEEE 802.15.4z. Tras esto, se han analizado los componentes de la tecnología 45RFSOI para, a continuación, proceder a realizar el diseño del esquemático del circuito. Este diseño se completa realizando una comparación de rendimiento entre los transistores proporcionados por la tecnología y añadiendo el resto de componentes, cada uno con una función determinada. Asimismo, el diseño se lleva a cabo tanto con componentes ideales, como con componentes del PDK. Por último, se realiza el diseño de layout del LNA, definiendo el floorplaning del circuito.

## Herramientas utilizadas

- Cadence Virtuoso

- Kit de diseño 45RFSOI de GlobalFoundries

- Ordenador personal

- Servidores de cómputo del **IUMA**